REFERENCE COPT

05EC021

REFERENCE COPY

| •    |     |  |  | <br> | <br> |  |

|------|-----|--|--|------|------|--|

| Reg. | No. |  |  |      |      |  |

# First Semester M.Tech. Degree Examination, January/February 2006 LDS/LEC/LVS/LPE/LIE/LEL CMOS VLSI Design.

Time: 3 hrs.)

(Max.Marks: 100

Note: Answer any FIVE full questions.

- (a) Describe the working on nMOS enhancement mode transistor with diagrams and output characteristics.

(8 Marks)

- (b) Deduce high frequency small signal equivalent circuit of MOS transistor and an expression for figure of merit.

(6 Marks)

- (c) What are the advantages of BiCMOS inverter over CMOS counterparts? Draw the circuit diagram of a BiCMOS inverter in which problems associated with static power dissipation and stored charge in the base are eliminated and explain its working.

(6 Marks)

- 2. (a) Explain  $\lambda$  based design rules as applicable to MOS layers and transistors. (8 Marks)

- (b) Compare CMOS and SOI technology. Draw sketches involved in CMOS inverter fabrication process.

(6 Marks)

- (c) Define sheet resistance, standard unit of capacitance and delay unit of time.

(6 Marks)

- 3. (a) Show that nMOS/CMOS inverter pair delay is invariant.

(6 Marks)

- (b) A MOS layer is  $5\lambda$  wide,  $60\lambda$  long and  $1\mu m$  thick. The resistivity of the layer is  $1\Omega cm$ . Using sheet resistance concept, calculate the resistance of the MOS layer along its length. (6 Marks)

- 4. (a) Derive an expression for the propagation delay through a chain of pass transistors.

(6 Marks)

- (b) Draw circuit and stick diagrams of two input NOR gate and 1 bit shift register using CMOS inverters. Standard colour/monochrome codes are to be used for stick diagrams.

(8 Marks)

- (c) Derive scaling factors of the following MOS parameters using combined voltage and dimension scaling model:

- i) Number of gates N

- ii) Saturation current  $I_{dss}$

- iii) Power speed product  $P_{T}$

(6 Marks)

Contd.... 2

5. (a) Distinguish between combinational and sequential circuits.

(4 Marks)

- (b) Describe the behaviour of two inverter bistable element with one inveter in the feed back loop. Also derive expressions for output voltages of inverters. (10 Marks)

- (c) Differentiate between static and dynamic CMOS circuits with relevant diagrams. (6 Marks)

- 6. (a) Explain how domino circuits evolved from dynamic CMOS circuits and reasons

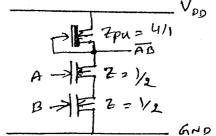

- (b) Draw nMOS and CMOS version of the circuit to realise the following Boolean expression:

(8 Marks)  $z=\overline{A(D+E)+BC}.$

- (c) Explain the working of clocked SR latch with the help of circuit diagram and waveforms. (6 Marks)

- 7. (a) What is latch up in CMOS inverters and how is it minimised? (8 Marks)

- (b) Realise NOR and NAND gate functions using transmission gates.

- (c) What are the demerits of n and p pass transistors w.r.t output voltages and how (6 Marks) are these overcome in a transmission gate?

- Write short notes on : 8.

- (a) MOS model

- (b) Differential amplifier

- (c) Clock generation and distribution

- (d) Voltage boot strapping.

(4×5=20 Marks)

|     | <br> | <br> | <br> |  |  |

|-----|------|------|------|--|--|

| USN |      |      |      |  |  |

#### **NEW SCHEME**

#### M.Tech. Degree Examination, May / June 2006

#### **CMOS VLSI Design**

Time: 3 hrs.] [Max. Marks:100

Note: Answer any FIVE full questions.

- a. Explain the trends in transfer characteristics with  $\beta_n/\beta_p$  ratio's, using suitable mathematical analysis.

- b. Write an expression for threshold voltage of n channel E-MOSFET and hence explain the role of each term in the equation. Modify this equation suitably so as to express the same for  $V_{SB} = 0$  (10 Marks)

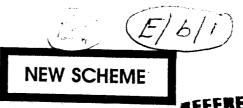

- 2 a. Estimate the ON state resistance of the inverter circuit shown in figure 2(a), using the concepts of sheet resistance. Assume 5  $\mu$  m technology. Given the following data, also estimate current between power lines. Derive the formula used for calculations.

| LAYER                | R <sub>S</sub> ohm per square |                   |                   |

|----------------------|-------------------------------|-------------------|-------------------|

|                      | 5 μ m                         | orbit             | orbit $1.2 \mu$ m |

| n-transistor channel | 10 <sup>4</sup>               | $2 \times 10^4$   | $2 \times 10^4$   |

| p-transistor channel | $2.5 \times 10^4$             | $4.5 \times 10^4$ | $4.5 \times 10^4$ |

- b. Explain the significance of channel length modulation and hot electron effect in MOS devices. (10 Marks)

- a. Explain the operation of MOSFET in CS configuration when the load to the devices are i) Resistive load, ii) Diode connected load, iii) Current source load.

(15 Marks)

Contd...2

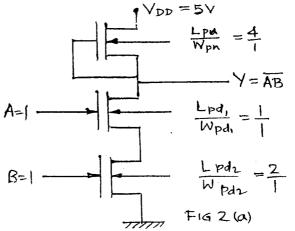

b. For the circuit shown in figure 3(b), calculate the small signal voltage gain of the circuit.

- a. Explain the fabrication process of P well CMOS inverter with neat sketches where ever necessary.

(10 Marks)

- b. What are lambda based design rules? Bring out the merits and demerits there of.

(10 Marks)

- 5 a. Draw symbol diagram of a two bit CMOS shift registers, reducing the number of transistors wherever possible.

- b. Draw nMOS, CMOS version of the circuit to realise the boolean expression. Z = (D + E + A)(B + C)(10 Marks)

- 6 a. Derive an expression for figure of merit of n channel E-MOSFET. (10 Marks)

- b. Explain the working of CMOS transmission sate with its equivalent resistance curve. What are the advantages of transmission gate? (10 Marks)

- 7 a. What is domino CMOS logic? Compare it with conventional CMOS logic. Justify the same with one example each. (10 Marks)

- b. Explain how clock signal can be generated, distributed and stored in dynamic CMOS inverter circuits. (10 Marks)

- 8 Write technical note on the following:

- a. Bi-CMOS inverter

- b. Pass transistor circuit

- c. Punch through conditions in MOS transistor.

- d. CMOS D latch.

(20 Marks)

\*\*\*\*

FJ 6/3

A. T. G. E. MERARY

|  | USECU. | ر ک |

|--|--------|-----|

|  |        |     |

|  |        |     |

| USN |

|-----|

|-----|

#### **NEW SCHEME**

## First Semester M.Tech. Degree Examination, Dec.06/Jan. 07 CMOS VLSI Design

Time: 3 hrs.] [Max. Marks:100

Note: 1. Answer any FIVE full questions.

- 2. Assume missing data if any.

- 3. Draw neat diagrams where ever necessary.

- 4. Show complete solutions to the derivations/problems step by step.

- 1 a. Write an expression for threshold voltage of n channel E MOSFET and hence explain the significance of each term in this equation. Also explain the concepts of sub threshold voltage and sub threshold current. (10 Marks)

- b. Draw a neat circuit of biased n channel E MOSFET operating in inversion mode and hence explain the concept of hot electron effect and punch through conditions, suggest any remedy if any to over come the problem of hot electron effect. (10 Marks)

- 2 a. Explain the transfer plot of CMOS inverter with necessary mathematical analysis for different values of  $\beta n / \beta p$  ratios. (10 Marks)

- Calculate the native threshold voltage for a n channel MOSFET at 300K for a process with a silicon substrate with Na =  $1.80 \times 10^{16}$ , a SiO<sub>2</sub> gate oxide with thickness 200Å. Assume  $\Phi_{ms} = -0.9$  volts,  $Q_{fe} = 0$ . (10 Marks)

- 3 a. With suitable mathematical analysis explain the transfer plot of MOS inverter with static load and pseudo n MOS inverter for different values of aspect ratios. (10 Marks)

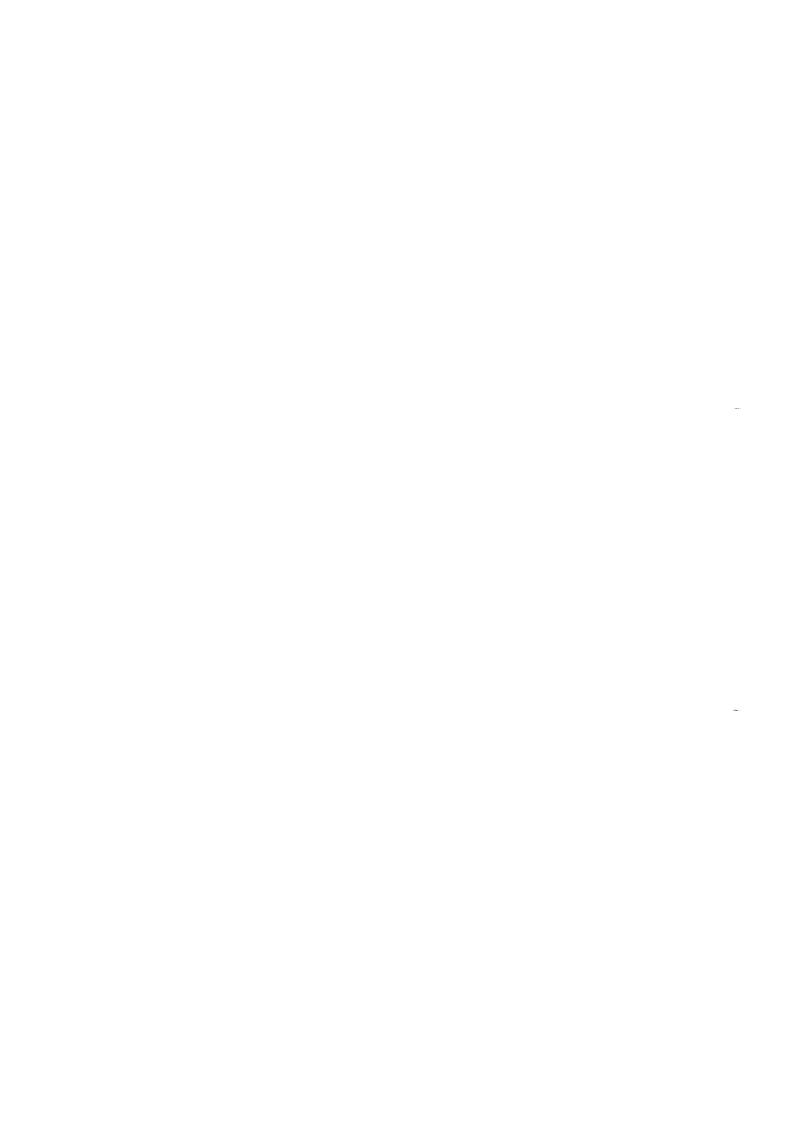

- b. Explain in detail the double metal MOS process rules for a VLSI technology.

(10 Marks)

- 4 a. Describe in detail twin well CMOS process of fabrication. (10 Marks)

- b. Calculate the time for free electrons to cross a n channel E MOSFET of channel length 3 microns. If Vdd = 5V, assume saturation velocity of electrons,

=

$$V_n = 5 \times 10^7$$

cm/sec and mobility of electrons =  $800 \text{ cm}^2 / \text{V} - \text{sec}$ . (10 Marks)

- 5 a. Show that as the RC delay lines approach infinity, the signal delay reduces when inverters are connected in cascade. (10 Marks)

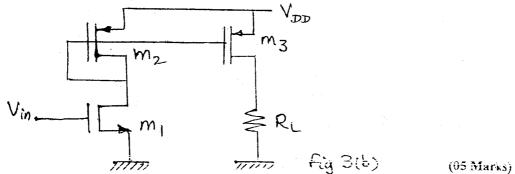

- b. Draw stick diagram for the following:

(i) (ii) (10 Marks)

Contd... 2

- 6 a. With neat diagrams explain the construction and working principles of voltage bootstrapping synchronous dynamic circuit. (10 Marks)

- b. Describe the construction and working principles of MOS differential amplifier driven by a constant current source and hence derive an expression for voltage gain of the amplifier.

- 7 a. Describe with neat figures the fabrication of N WELL CMOS.

(10 Marks)

b. Explain the operation of CMOS SR Latch and clocked JK Latch

(10 Marks)

- 8 Write technical notes on the following:

- a. SOS technology.

- b. Clocked storage elements.

(20 Marks)

\*\*\*\*

**USN**

(07 Marks)

#### **NEW SCHEME**

## First Semester M.Tech. Degree Examination, June 2007

|   |          | That Semester M. Tech. Degree Examination, June                                                                                                                                                                                                  | 2007                                                          |

|---|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

|   | Tim      | e: 3 hrs.]                                                                                                                                                                                                                                       |                                                               |

|   |          | Note: Answer any FIVE full questions [Ma                                                                                                                                                                                                         | x. Marks:100                                                  |

|   | 1        | a. Starting from the fundamentals, derive an expression for threshold volt transistor.                                                                                                                                                           | age in a MOS                                                  |

|   |          | <ul> <li>b. Briefly explain the following terms: i) Channel length modulation ii) Fow tunneling iii) Impact ionization.</li> <li>c. With a neat diagram showing the levels of various voltages and transfer explain the noise margin.</li> </ul> | ler – Nordheim<br>(08 Marks)                                  |

| 2 | ;        | a. Explain the working of differential inverter with a neat diagram an                                                                                                                                                                           | (06 Marks)  d the transfer                                    |

|   | (        | <ul> <li>b. With respect to: i) Change in control input ii) Change in switched input transmission gate output characteristics.</li> <li>c. Discuss the various circuit arrangements to be employed in BICMOS invertigation.</li> </ul>           | (06 Marks) it, explain the                                    |

| 3 |          | Explain with neat sketches the lambda bared design rules with resp<br>transistors and contacts.  With a neat structure (final diagram) explain the twin tub CMOS                                                                                 | (08 Marks) ect to wires, (08 Marks) (06 Marks) fractory metal |

| 4 | a        | construct the transit time and time delay are interchangeable in CMOS                                                                                                                                                                            | (06 Marks) S technology.                                      |

|   | b<br>c.  | Derive an expression for total delay when number of stages N is odd an driving large capacitive loads.                                                                                                                                           | (08 Marks)<br>d éven while                                    |

| 5 | a.       | With a neat CMOS circuit diagram showing the parasitic consistence                                                                                                                                                                               | (04 Marks)                                                    |

|   |          | of took gate and specify the condition for K <sub>n</sub> and K <sub>n</sub> to get V <sub>1</sub> - V <sub>DD</sub>                                                                                                                             | /                                                             |

|   | b.       | (O-A-I) logic with a suitable example                                                                                                                                                                                                            | ND-inverter                                                   |

|   | ٥.       | Explain briefly the SR latch with gate level schematic truth tables and Cl                                                                                                                                                                       | MOS circuit.                                                  |

| 6 | a.       | Explain the phenomenon of charge storage and charge leakage and obtain the                                                                                                                                                                       | (07 Marks)<br>e expression                                    |

|   | b.<br>с. | Dynamic CMOS logic circuits cannot be cascaded. Why? Explain.  Discuss the pipelined NORA CMOS system with relevant diagrams.                                                                                                                    | (07 Marks)<br>(06 Marks)                                      |

| 7 | a.       | Explain the differential amplifier with a post CMOS                                                                                                                                                                                              | (O# > #                                                       |

|   | b.       | expression for transconductance of differential amplifier.  Starting from the fundamentals derive an expression for the reference voltage conventional CMOS band gap reference.                                                                  | (10 Marks)<br>ge V <sub>REF</sub> in a                        |

| 8 | a.       | Explain the latch up phenomenon in a CMOS attract                                                                                                                                                                                                | (10 Marks)                                                    |

|   | b.       | view, circuit model and V-I characteristics.  Bring out the differences between NMOS and CMOS fabrication processes.  Explain the various techniques employed for generation of clock in CMOS to                                                 | (08 Marks)                                                    |

05EC021

## SN

## M.Tech. Degree Examination, Dec. 07 / Jan. 08 CMOS VLSI Design

Time: 3 hrs.

Max. Marks:100

Note: Answer any FIVE full questions.

1 a. Briefly explain the second order effects in MOSFET.

(07 Marks)

- b. With neat diagram and transfer characteristics, explain the CMOS inverter. Obtain the necessary expressions for the same. (08 Marks)

- c. Calculate the native threshold voltage for an n-transistor at  $300^{\circ}$  k for a process with a silicon substrate with  $N_A = 1.8 \times 10^{16}$  /cc,  $t_{ox} = 200 \, \text{Å}$ . Assume  $\phi_{ms} = -0.9 \, \text{V}$ ,  $Q_{fc} = 0$ ,  $\eta_I = 1.45 \times 10^{10}$  /cc. (05 Marks)

- 2 a. With relevant response curves, explain the transmission gate output characteristics for change in control input and for change in switched input. (06 Marks)

- b. Obtain the scaling factors for the following i) Gate delay ii) Current density iii) Switching energy.

(06 Marks)

- c. With neat fabrication sketches. Explain the silicon on insulator (SOI) COMS process.

(08 Marks)

- 3 a. Explain the CMOS process enhancement with reference to i) metal interconnect ii) polysilicon/refractory metal inter connect. (06 Marks)

- b. For the following structure obtain values for Cm, Cp, Cg and C<sub>T</sub>. Given that the relative values of capacitances are metal  $1 = 0.075 \square Cg$ , polysilicon =  $0.1 \square Cg$ .

Fig. Q 3(b)

(08 Marks)

c. Obtain the CMOS circuit and stick diagram for the following function f = (A + BC)D.

(06 Marks)

- 4 a. With a neat diagram, obtain the parasitic device capacitance in CMOS 2 input NOR gate for kN = 4 KP and explain the circuit operation. (06 Marks)

- b. Differentiate between AOI logic and OAI logic with a suitable example of each. (08 Marks)

- c. For the given function F = AB + A'C' + AB'C obtain the i) CMOS TG realization

- ii) COMS transistor realization.

(06 Marks)

- 5 a. With a neat gate level schematic and CMOS circuit explain the CMOS SR latch circuit based on clocked NOR2 gates.

- b. Briefly discuss the charge storage and charge leakage in n mos pass transistor. (06 Marks)

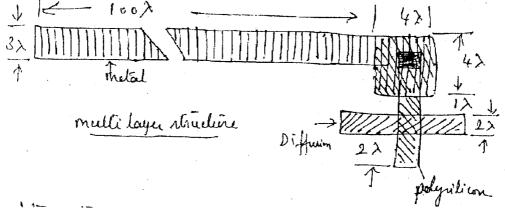

- c. Calculate the worst case time for the following data given  $V_{TO}=0.8~V,~\nu=0.4~V^{\frac{1}{2}},~|2\phi_F|=0.6V$ ,  $C_{OX}=0.065~f$  F / $\mu$  m $^2$ ,  $C_{metal}^1=0.036f$  F / $\mu$ m $^2$ ,  $C_{poly}^1=0.055f$  F / $\mu$ m $^2$ ,  $C_{jo}=0.095~f$  F/ $\mu$  m $^2$ ,  $C_{josw}=0.2~f$  F/ $\mu$  m.  $I_{leakage}=0.85~p$ A.

Fig. Q 5(c)

(08 Marks)

- 6 a. Bring out the difference between Ratioed logic and ratio less logic with respect to 3 bit shift register. (06 Marks)

- b. Dynamic CMOS logic circuit cannot be cascaded. Justify the statement.

(06 Marks)

- c. With relevant diagram, explain the NORA CMOS logi e[NP Domino logid].

- (08 Marks)

- 7 a. Explain with necessary expressions and transfer characteristics the differential amplifier.

(08 Marks)

- b. Discuss the general principle of the Band-gap reference and hence obtain expression for V<sub>BE</sub>.

(07 Marks)

- c. Briefly explain the clock distribution network with relevant sketches.

(05 Marks)

8 Write short notes on:

(10 Marks)

- a. Differential inverter

- b. Complementary pass transistor logic (CPL)

- c. Domino CMOS logic

- d. Latch up phenomenon.

(10 Marks)

\*\*\*\*

1

2

4

b. Draw the emos circuit and stick diagram for the function  $\overline{(AB+C)D}$ . (06 Marks)

What are the disadvantages of nmos and pmos pass transistors? How is the transmission gate useful in this regard? (04 Marks)

5 With a neat circuit diagram, showing the parasitic capcitance, explain cmos 2 input NOR gate and specify the condition for Kn and Kp to get  $Vth = \frac{VDD}{2}$ . (08 Marks)

b. Realize the functions,

A = xy + x'y' + xy'z and

B = x'y + xy'

using transmission gates.

(06 Marks)

Draw the emos logic circuit for the function (D+E+A)(B+C)=Z.

(06 Marks)

6 Explain the function of a SR latch using NAND2 gates with gate level schematic and cmos circuit. (06 Marks) b. What is voltage boot strapping? Explain.

(08 Marks)

c. Explain the phenomenon of charge storage and charge leakage in a nmos pass transistor.

(06 Marks)

7 Explain the operation of a cmos differential amplifier with neat circuit. (08 Marks)

b. Describe the different clock distribution schemes.

(06 Marks)

With neat circuit diagram explain NORA CMOS logic (NP - Domino logic).

(06 Marks)

8 Write short notes on:

a. Domino cmos logic.

b. Bicmos circuits.

c. Cmos process enhancement.

S.O.I technology.

(20 Marks)

## REFERENCE COMY M.Tech. Degree Examination, Dec.09/Jan.10. V. G. C. E. LIERARY

#### **CMOS VLSI Design**

With neat sketches, explain the behaviour of nMOS device under the influence of different ĺ terminal voltages (Enhancement mode).

Explain small signal model for an MOS transistor.

(06 Marks)

Max. Marks:100

Write a note on differential inverter.

(05 Marks)

Explain  $\lambda$  based design rules. a.

(08 Marks)

- Obtain the scaling factors for the following:

- Gate capacitance Cg

- ii) Saturation current Idss

- iii) Parasitic capacitance.

(06 Marks)

- Define sheet resistance and also explain the concept applied to MOS transistor and inverters. (06 Marks)

- Explain the second order effects associated with a MOSFET.

(10 Marks)

Explain twin tub CMOS process. b.

(10 Marks)

Explain the effect of long polysilicon wires. Show how to improve the signal propagation.

- Derive the threshold voltage equation (V<sub>t</sub>) for 2 inputs CMOS NOR gate (V<sub>t NOR2</sub>).(10 Marks)

- For the given function  $f = \overline{AB} + A\overline{C} + A(B+D)$ , obtain

- CMOS TG realization

- ii) CMOS transistor realisation

(06 Marks)

Explain the function of D latch with gate level schematic and CMOS circuit.

(06 Marks)

Explain synchronous dynamic circuit implemented using depletion load nMOS.

(09 Marks)

Explain the principle of pass transistor circuit.

- (05 Marks)

- Discuss the general principle of band gap reference and hence obtain expression for V<sub>BE</sub>. a.

(08 Marks)

- Explain cross operational amplifier with necessary expression and characteristics. (08 Marks)

- Mention the advantages of CMOS over NMOS.

(04 Marks)

Describe different clock distribution schemes.

(06 Marks)

Mention the causes of latch up and guidelines for avoiding latch up.

(10 Marks)

- Realize the following function Z = AB + (C + D)(E + F) + GH using

- Standard CMOS i)

- ii) Domino CMOS.

(04 Marks)

- Write short notes on: 8

- **BICMOS** circuit a.

- b. Dynamic CMOS logic

- Voltage boot strapping

- Current mirror.

(20 Marks)